A note on using PllLdr with AD9850/51 DDS chips.

PllLdr is a generic microcontroller to load a PLL chip’s configuration registers using SPI. SPI is used by many PLL and DDS chips, data format and content varies from chip to chip.

The AD9850 powers up in parallel load mode, and AD gives advice on how to get it into serial load mode (as you would use with PllLdr).

Wire chip pin 2 to ground, and pins 3 and 4 to Vcc.

Configure PllLdr with an empty first register in each slot.

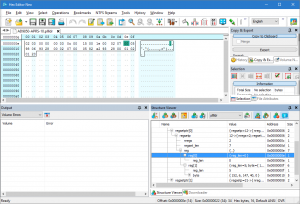

Here is a configuration for an APRS FSK modulator on the 30m band. Note that in each slot, there are two registers defined, but the first one is empty.

{

"ver":"02",

"rbo":"R",

"options":["0300","0000"],

"regs":[

["","0014C96019"],

["","0014C94541"],

["04"]

]

}

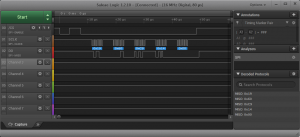

The empty register will cause PllLdr to cycle the /CS line but not clock any data into the DDS.

Above, the /CS line cycles once putting the DDS into serial load mode, and the next cycling of /CS includes data being clocked into the DDS. (Note that the data is sent LSB first.) It appears that the rise of W_CLK (SCLK) on power up parallel loads the hard wired bits to W0 and sets serial mode on the rising edge of the first FQ_UD (/CS) from PllLdr.

The EEPROM data structures for this case are shown above.

This method seems to reliably ensure that the DDS switches to serial mode on the first data load after power up.